实现高效的混合模型执行

(中国AI网 2025年09月01日)低延迟与低功耗的边缘AI对于增强/虚拟现实应用至关重要。 近期进展表明,结合卷积神经网络和ViT的混合机器学习模型,通常能实现更优的精度/性能权衡。然而,混合ML模型由于其数据流和内存访问模式的多样性,可能会在延迟和能效方面带来系统性的挑战。

在一项研究中,卡内基梅隆大学,Meta,纽约大学,以及康奈尔大学纽约科技校区团队利用神经处理单元和CIM的架构异构性,并探索多样化的执行方案以实现高效的混合模型执行。

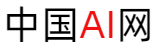

团队提出了H4H-NAS,这是一个两阶段的神经架构搜索(NAS)框架,用于自动设计面向同时具备NPU和CIM的异构边缘系统的混合CNN/ViT模型。他们在NAS中提出了一个两阶段的增量式超网训练方法以提高模型精度。H4H-NAS方法同时配备了一个性能估算器,而所述估算器基于真实硅芯片测量的NPU性能结果以及基于行业IP的CIM性能数据。H4H-NAS在ImageNet-1k分类任务上实现了显著的(最高达1.34%)Top-1精度提升,以及最高达56.08%的整体延迟降低和41.72%的能耗降低。

增强现实/虚拟现实正日益成为关键的下一代人本计算平台。 然而,大多数AR/VR设备通常具有有限的计算能力、内存容量和功耗预算,但由于AR/VR应用的需求(如手势追踪和检测),又需要完成超低延迟的本地ML推理。同时,为了提高任务性能,用于相关应用的ML模型正变得越来越多样化。

例如,在计算机视觉领域,ResNet、MobileNet-v2 和ViT的基本块结构差异巨大,需要在硬件上具备灵活的执行方案。这种多样性给设计能效跨越各种模型的通用加速器带来了挑战:为某一代模型高度优化的加速器,在新模型上可能效率降低。在严格的能耗/延迟要求下,涌现了各种边缘AI加速设计来应对这些挑战:

NPU: 神经处理单元NPU已成为在边缘设备严格资源限制下加速计算密集型工作负载的流行解决方案。通常,NPU采用脉动阵列作为其核心组件,以高效计算矩阵乘法。

CIM: 然而,随着计算能力的提升,内存与处理器之间频繁的数据移动主导了能耗/延迟成本。为了缓解这个问题,存内计算CIM重新兴起,以有效减少数据移动。在CIM中,计算单元靠近存储器(近存计算)甚至与存储器融合(内存计算),从而提升延迟/能效。CIM推动了基于ReRAM、PCM、MRAM、DRAM等技术的AI/ML及其他工作负载相关加速器的设计。

随着ML算法/模型和边缘硬件加速器这两方面的多样化进展,当前边缘AI/ML系统的设计空间变得极其复杂。在这项研究中,团队提出了一种结合NPU和CIM的通用设计方案,利用NPU和CIM的架构异构性,并通过混合CNN/ViT模型产生的多样化数据流来加速边缘AI。

另外,团队引入了一个以神经架构搜索为核心的自动化设计流程来协同设计混合CNN/ViT模型,以在异构架构上实现最佳的精度/性能权衡。

在研究中,他们专注于协同设计由NPU和CIM组成的混合模型与异构系统,为高效的边缘AI/ML提供潜在解决方案。团队开发了一个名为H4H的工作流程,用于自动化算法和硬件的协同设计,以在配备NPU和CIM的异构边缘系统使用混合的CNN+ViT模型进行高效推理。

神经架构搜索(NAS)是一种高效的方法,可自动化设计大量DNN以发现适合移动部署的高效解决方案。团队遵循两阶段的OFA-NAS框架开发了H4H-NAS——第一阶段进行超网训练,第二阶段进行子网搜索。重点是支持混合模型的灵活搜索空间,并将其部署在异构的NPU+CIM架构。

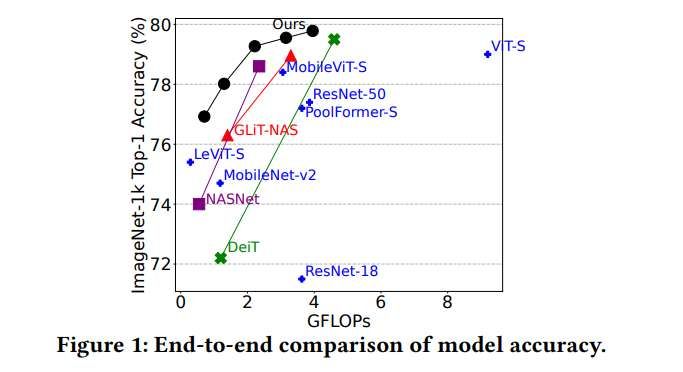

他们使用重复的“卷积 + transformer”块构建了超网结构。如图2所示,超网可以灵活地缩减为纯CNN模型(如MobileNetv2)、纯ViT模型或类似于先前NAS研究的“CNN在前ViT在后”结构。这种设计确保了超网架构的灵活性,使其在搜索过程中能够缩减为各种模型类型中的最佳模型模式。

当直接使用标准的NAS训练方案时,可以观察到在大型混合(CNN+ViT)搜索空间中,子网的性能比在较小的纯CNN空间中更差。类似的现象在先前的研究中同样有观察到。这种性能下降很可能源于训练期间不同采样子网的梯度未对齐。他们进一步观察到,在混合搜索空间中,这种梯度冲突/未对齐现象被不同块类型所放大。

为了解决这个梯度冲突问题,团队提出了一种名为“两阶段增量式超网训练”的新训练方案。超网训练阶段分为两个阶段。在第一阶段,从超网中移除所有ViT块,仅使用所有剩余的CNN组件训练一个部分超网(即首先训练一个纯CNN超网)。

在第二阶段,将第一阶段所有预训练的CNN权重加载到完整的混合超网中,并继续训练。其基本思路是,在每个阶段中,仅属于同一类型的块一起训练。因此,梯度冲突应在每个阶段内得到缓解。

一旦超网训练完成,采用进化搜索来寻找最优子网,同时考虑严格的系统能耗/延迟约束。团队对在异构AI边缘设备运行的子网进行建模。系统模型将ML模型分解为细粒度组件。对于卷积层,它将不同通道的执行分配到不同的设备上。类似地,对于transformer层,它将Q/K/V的生成以及注意力层中不同头的执行进行划分。系统建模工具结合了使用定制硅芯片的测量结果和工业CIM IP的仿真结果。另外,模拟了通过片上网络在NPU和CIM之间进行数据传输所引起的延迟/能耗。因此,为目标子网获得了精确的延迟和能耗估计。

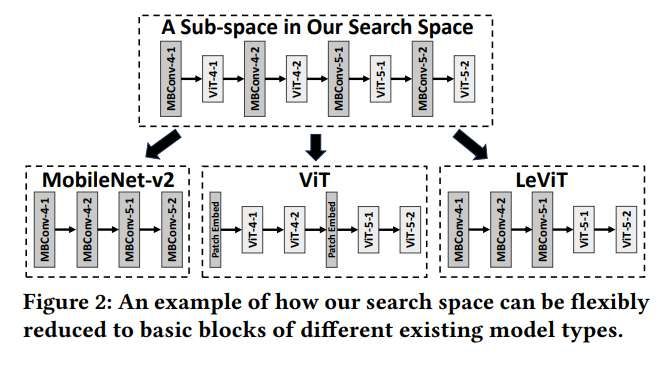

为了实现边缘ML推理的并行执行,将多个CIM宏单元聚合到一个系统中,同时并行化大型模型层的计算。另外,在单个CIM宏单元内引入了多个计算单元,如图3(右)所示。这种设计不仅提高了吞吐量,而且能将重复的输入数据合并并传输到同一个CIM宏单元中。输入特征图(IFMP)控制器以较低的面积开销(< 0.1%)重新组织计算所需的数据流。

在评估时,结果基于U55 NPU 的真实硅芯片测量数据和SPICE仿真的工业MRAM-CIM IP。图1显示,与先前方法相比,H4H-NAS方法显著提升了ImageNet-1k分类的精度/延迟前沿。例如,在相同的延迟要求下,配备8个CIM宏单元的H4H设计系统支持的混合模型,其Top-1精度比纯NPU系统高出1.34%。同时,对于精度相同的模型,配备8个CIM宏单元的系统进行推理的平均延迟降低了21.99%,最高可达56.08%。

相关论文:H4H: Hybrid Convolution-Transformer Architecture Search for NPU-CIM Heterogeneous Systems for AR/VR Application

https://dl.acm.org/doi/pdf/10.1145/3746238.3746241

对于节能效果,在相同的能耗要求下,配备8个CIM宏单元的系统可以支持精度高出0.614%的混合模型。此外,它实现了平均11.80%、最高33.13%的能耗降低。在一个CIM宏单元内配备4个计算单元的情况下(图3),与纯NPU系统相比,能耗平均降低了19.11%,最高可达41.72%。

有趣的是,H4H-NAS倾向于同时包含CNN和ViT,并在它们之间保持平衡以实现高效推理。几乎所有搜索到的子网都呈现出类似的比例:2-5个ViT块与10个CNN块组合。这一现象表明,具有固定比例的CNN和ViT的重复块组合是更优的选择。